ę╗Īó▀mė├ĘČć·Ż║

įōīŹ(sh©¬)“×(y©żn)ŽĄĮy(t©»ng)▓╗āHßśī”(du©¼)CPLD/FPGA/SOPC╚ļķT╩╣ė├║═║å(ji©Żn)å╬įO(sh©©)ėŗ(j©¼)æ¬(y©®ng)ė├, Č°Ūęī”(du©¼)ė┌│╠Č╚▌^Ė▀Ą─═¼īW(xu©”), įōŽĄĮy(t©»ng)╠ß╣®┴╦śOŲõžSĖ╗Ą─╣”─▄å╬į¬║═öU(ku©░)š╣å╬į¬Ż¼Ė„╣”─▄å╬į¬┐╔ęįņ`╗ŅĮM║Ž, ╩╣╦¹éā─▄ē“ū÷│÷│¼│÷┤¾ŠVę¬Ū¾Ą─Š▀ėąÅ═(f©┤)ļsąį║═äō(chu©żng)įņąįĄ─ŠC║ŽīŹ(sh©¬)“×(y©żn).

įōŽĄ┴ąīŹ(sh©¬)“×(y©żn)įO(sh©©)éõ╠žäe▀m║Žė┌Ė▀ąŻEDAīŹ(sh©¬)“×(y©żn)Į╠īW(xu©”)╝░"¼F(xi©żn)┤·öĄ(sh©┤)ūųļŖūė╝╝ąg(sh©┤)"Ą╚šn│╠Ą─īŹ(sh©¬)“×(y©żn)Į╠īW(xu©”)Īó«ģśI(y©©)įO(sh©©)ėŗ(j©¼)╝░┤¾īW(xu©”)╔·ļŖūėįO(sh©©)ėŗ(j©¼)Ėé(j©¼ng)┘ÉĄ╚Ż¼═¼Ģr(sh©¬)įōŽĄĮy(t©»ng)ę▓╩ŪÅ─╩┬Į╠īW(xu©”)╝░┐Ų蹥─ÅV┤¾Į╠Ĥ║═ļŖūė╣ż│╠ĤéāĄ─└ĒŽļķ_░l(f©Ī)╣żŠ▀ĪŻ

Č■ĪóĮY(ji©”)śŗ(g©░u)║å(ji©Żn)ĮķŻ║

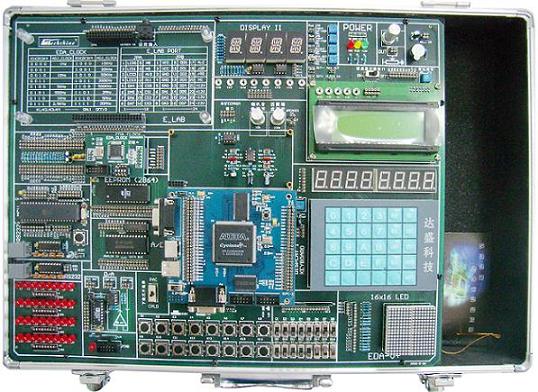

EDA-V+ą═īŹ(sh©¬)“×(y©żn)ŽĄĮy(t©»ng)ė▓╝■ė╔öĄ(sh©┤)ūųŻ©CPLD/FPGA/SOPCŻ®┐╔ŠÄ│╠Ų„╝■ų„ąŠŲ¼║═Ė„īŹ(sh©¬)“×(y©żn)?z©Īi)ŻēKśŗ(g©░u)│╔,ų„ąŠŲ¼┐╔Ė∙ō■(j©┤)ė├æ¶ąĶę¬ūį╝║▀xō±,─┐Ū░įōŽĄĮy(t©»ng)ų¦│ųALTERAĪóXILINXĪóLATTICE╣½╦Š▓╗═¼ŽĄ┴ąĪó▓╗═¼ļŖē║1.5V\2.5V\3.3V\5VĪó▓╗═¼ķTöĄ(sh©┤)ęÄ(gu©®)─ŻĄ─ąŠŲ¼Ż¼Ė„īŹ(sh©¬)“×(y©żn)?z©Īi)ŻēK╝╚┐╔¬Ü(d©▓)┴óīŹ(sh©¬)“×(y©żn), ę▓┐╔ĮM║ŽīŹ(sh©¬)“×(y©żn), Š▀ėąĘŪ│ŻĖ▀Ą─ņ`╗ŅąįŻ¼ķ_Ę┼ąį║═┐╔ķ_░l(f©Ī)ąįĪŻ

|